技術部の番場博則さんが2023 VLSI Test of Time Awardを受賞

2023年6月13日、当社技術部の番場博則さんが、VLSIシンポジウムでTest of Time Awardを共著者6名の方々と共に受賞しました。

VLSIシンポジウム(Symposium on VLSI Technology and Circuits)は最先端半導体デバイスプロセス技術、回路技術に関する最高峰の国際学会の1つです。

“Test of Time Award” は10年以上前にVLSIシンポジウムで発表され、時の試練(Test of Time)に耐え、歴史にその名を刻んだ、この分野に永続的な影響を与えた論文を表彰するものです。

1998年(当時東芝)に番場さんらのグループが発表した論文、“A CMOS Band-Gap Reference Circuit with Sub 1V Operation”(電源電圧1V以下で動作するCMOSバンドギャップリファレンス回路)が、表彰されました。

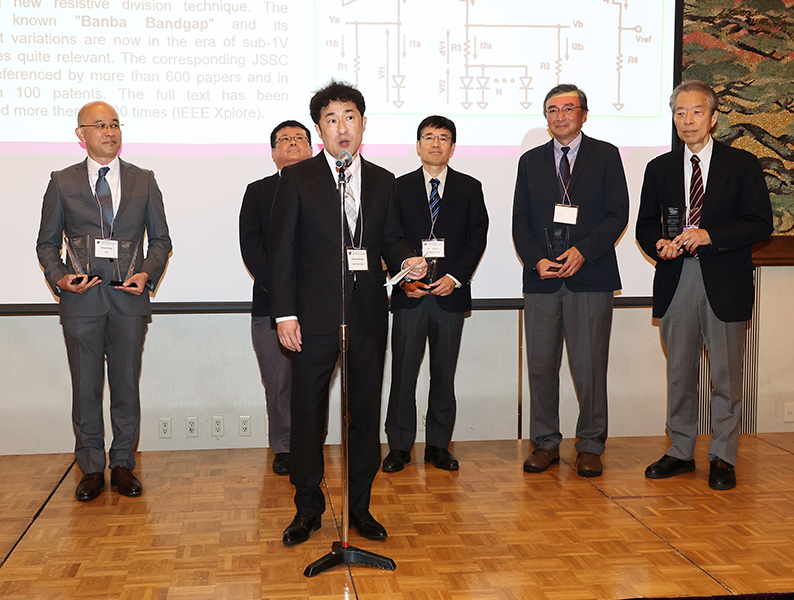

受賞者(番場さんは左から2人目)

受賞者(番場さんは左から2人目)

番場さんは筆頭著者として受賞スピーチをしました。

番場さんは筆頭著者として受賞スピーチをしました。

表彰楯

表彰楯

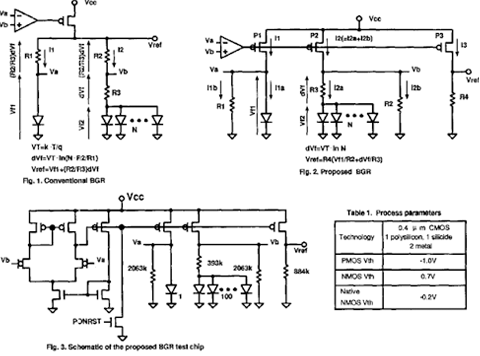

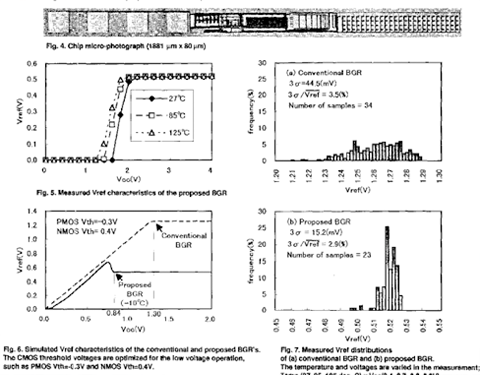

受賞論文

“A CMOS Band-Gap Reference Circuit with Sub 1V Operation”

本論文は、電源電圧1V以下で動作するCMOSバンドギャップリファレンス(BGR)回路(基準電圧回路)を提案しました。

従来のBGR回路では、出力電圧Vrefの設計値は約1.25Vとなり、LSIの低電源電圧化(1V以下)の要求に応えることが出来ていませんでした。

低電源電圧化は最先端LSIの微細化や低消費電力化の観点からも必須でした。

これに対し、番場さんが提案したBGR回路(通称、Banba Bandgap)では、回路内の電圧の加算ではなく電流の加算を行うことでVrefを下げ、1V以下での動作が可能となり、低電圧で動作する最も初期の実装の一つを提案しました。

この回路は世界中で多くのCMOSアナログ回路の教科書や論文等で参照され、対応するJSSC論文は600以上の論文と100以上の特許で参照されています。

IEEE Xploreでは21,000回以上ダウンロードされています。